纳米增材制制工艺可大幅降低芯片出产成本

为了降低电子产物和芯片的制形成本,团队开辟出一种增材自下而上的制制工艺。他们抽象地比方道,保守方式就像正在石头上凿刻出新事物;而新方好像用黏土建制新物体。新工艺无

为了降低电子产物和芯片的制形成本,团队开辟出一种增材自下而上的制制工艺。他们抽象地比方道,保守方式就像正在石头上凿刻出新事物;而新方好像用黏土建制新物体。新工艺无

Source:

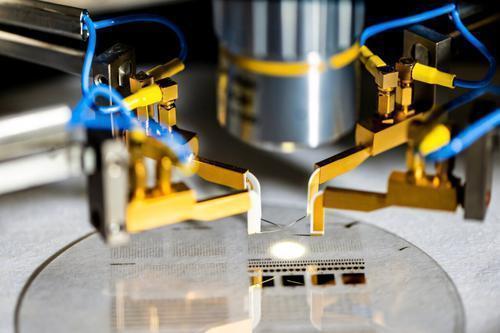

为了降低电子产物和芯片的制形成本,团队开辟出一种增材“自下而上”的制制工艺。他们抽象地比方道,保守方式就像正在石头上凿刻出新事物;而新方好像用黏土建制新物体。新工艺无需剔除任何材料,这些材料可利用很是小的颗粒快速堆积,可正在一分钟内建制出小至25纳米的布局。新方式不只产量高,并且成本极低。

据美国官网近日报道,该校研究团队开辟出一种新工艺及打印设备,能正在纳米标准上更高效地制制先辈的电子产物和芯片,其制形成本仅为保守手艺的1%。

保守微电子制制的根基流程是将材料堆积到薄膜内,再“蚀刻”掉多余部门。多层材料叠加建立,最终构成一个微处置器或存储芯片。并且,每种材料需要分歧工艺进行处置。

上一篇:国内木材市场:进口维持量贬价涨!

上一篇:国内木材市场:进口维持量贬价涨!